ऑटो ऑप्टिकल बीजीए रिवॉर्क्स स्टेशन

मोबाइल, लैपटॉप, कंप्यूटर, टीवी, एयर कंडीशनर आदि के मदरबोर्ड के लिए चिप-लेवल रिपेयरिंग में व्यापक रूप से उपयोग किया जाता है। इसमें रिपेयरिंग की उच्च सफल दर और ऑटोमेशन की उच्च डिग्री है और बहुत सारे मानव प्रयासों को बचाती है। हम इस मशीन के पेशेवर निर्माता हैं और यह मशीन स्टॉक में उपलब्ध है।

विवरण

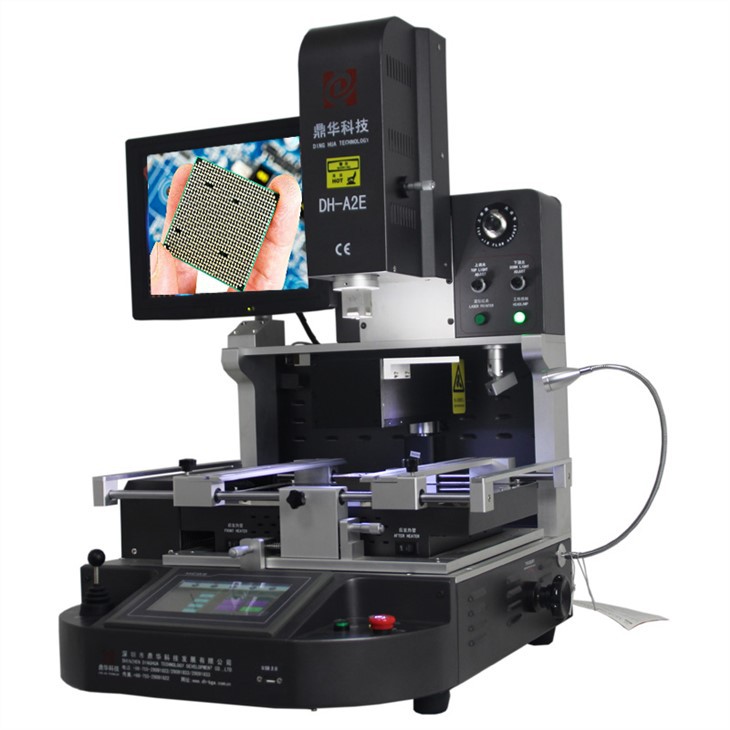

ऑटो ऑप्टिकल बीजीए रिवॉर्क्स स्टेशन

1. ऑटो ऑप्टिकल बीजीए रिवॉर्क्स स्टेशन का आवेदन

कंप्यूटर, स्मार्ट फोन, लैपटॉप, मैकबुक लॉजिक बोर्ड, डिजिटल कैमरा, एयर कंडीशनर, टीवी और अन्य इलेक्ट्रॉनिक का मदरबोर्ड

चिकित्सा उद्योग, संचार उद्योग, ऑटोमोबाइल उद्योग आदि से उपकरण।

विभिन्न प्रकार के चिप्स के लिए उपयुक्त: BGA, PGA, POP, BQFP, QFN, SOT223, PLCC, TQFP, TDFN, TSOP, PBGA, CPGA, LED चिप।

2. ऑटो ऑप्टिकल बीजीए रिवॉर्क्स स्टेशन की उत्पाद विशेषताएं

चिप स्तर की मरम्मत की उच्च सफल दर। डीसोल्डरिंग, माउंटिंग और सोल्डरिंग प्रक्रिया स्वचालित है।

• ऑप्टिकल संरेखण सीसीडी कैमरा के साथ प्रत्येक सोल्डरिंग जोड़ के सटीक संरेखण की गारंटी दी जा सकती है।

• सटीक तापमान नियंत्रण 3 स्वतंत्र हीटिंग क्षेत्रों के साथ सुनिश्चित किया जा सकता है। मशीन सेट और बचा सकती है

1 मिलियन तापमान प्रोफ़ाइल।

• डीसोल्डरिंग पूरी होने के बाद माउंटिंग हेड में बिल्ट-इन वैक्यूम स्वचालित रूप से बीजीए चिप को उठाता है।

3. ऑटो ऑप्टिकल बीजीए रिवॉर्क्स स्टेशन की विशिष्टता

4. ऑटो ऑप्टिकल बीजीए रिवॉर्क्स स्टेशन का विवरण

सीसीडी कैमरा (सटीक ऑप्टिकल संरेखण प्रणाली); 2. एचडी डिजिटल डिस्प्ले; 3. माइक्रोमीटर (चिप का कोण समायोजित करें);

4.3 स्वतंत्र हीटर (गर्म हवा और अवरक्त); 5. लेजर पोजीशनिंग; 6. एचडी टच स्क्रीन इंटरफ़ेस, पीएलसी नियंत्रण;

7. एलईडी हेडलैम्प; 8. जॉयस्टिक नियंत्रण।

5. हमारा ऑटो ऑप्टिकल बीजीए रिवॉर्क्स स्टेशन क्यों चुनें?

6. ऑटो ऑप्टिकल बीजीए रिवॉर्क्स स्टेशन का प्रमाण पत्र

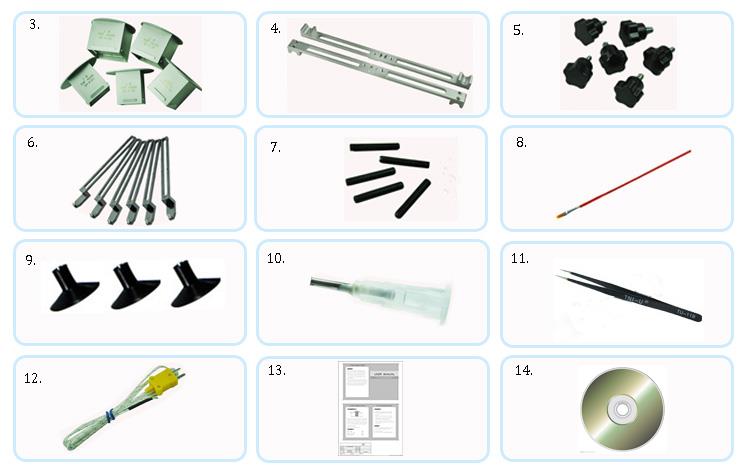

7. ऑटो ऑप्टिकल बीजीए रिवॉर्क्स स्टेशन की पैकिंग और शिपमेंट

8.अक्सर पूछे जाने वाले प्रश्न

चिप का परीक्षण कैसे करें?

प्रारंभिक प्रणाली-स्तरीय चिप परीक्षण

SoC गहरी सबमाइक्रोन प्रक्रियाओं पर आधारित है, इसलिए नए Soc उपकरणों का परीक्षण करने के लिए पूरी तरह से नए दृष्टिकोण की आवश्यकता होती है। क्योंकि प्रत्येक कार्यात्मक घटक

इसकी अपनी परीक्षण आवश्यकताएं हैं, डिज़ाइन इंजीनियर को डिज़ाइन प्रक्रिया के प्रारंभ में एक परीक्षण योजना बनानी चाहिए।

SoC उपकरणों के लिए ब्लॉक-बाय-ब्लॉक परीक्षण योजना लागू की जानी चाहिए: तर्क परीक्षण के लिए ठीक से कॉन्फ़िगर किए गए ATPG उपकरण; लघु परीक्षण समय; नई उच्च गति

गलती मॉडल और एकाधिक मेमोरी या छोटे सरणी परीक्षण। उत्पादन लाइन के लिए, निदान पद्धति न केवल दोष ढूंढती है, बल्कि इसे अलग भी करती है

कार्यशील नोड से दोषपूर्ण नोड। इसके अलावा, टेस्ट मल्टीप्लेक्सिंग तकनीकों का परीक्षण समय बचाने के लिए जब भी संभव हो उपयोग किया जाना चाहिए। अत्यधिक के क्षेत्र में

एकीकृत आईसी परीक्षण, एटीपीजी और आईडीडीक्यू की परीक्षण योग्य डिजाइन तकनीकों में एक शक्तिशाली दोष पृथक्करण तंत्र है।

अन्य वास्तविक पैरामीटर जिन्हें पहले से नियोजित करने की आवश्यकता है उनमें पिन की संख्या शामिल है जिन्हें स्कैन करने की आवश्यकता है और प्रत्येक पिन अंत में मेमोरी की मात्रा शामिल है।

बाउंड्री स्कैन को SoC पर एम्बेड किया जा सकता है, लेकिन यह बोर्ड या मल्टी-चिप मॉड्यूल पर इंटरकनेक्ट टेस्ट तक सीमित नहीं है।

हालांकि चिप का आकार कम हो रहा है, फिर भी एक चिप लाखों से 100 मिलियन ट्रांजिस्टर पैक कर सकती है, और परीक्षण मोड की संख्या में अभूतपूर्व वृद्धि हुई है

स्तर, जिसके परिणामस्वरूप परीक्षण चक्र लंबा हो जाता है। इस समस्या का परीक्षण किया जा सकता है। हल करने के लिए मोड संपीड़न, संपीड़न अनुपात 20 प्रतिशत से 60 प्रतिशत तक पहुंच सकता है। आज के बड़े पैमाने के लिए

चिप डिज़ाइन, क्षमता संबंधी समस्याओं से बचने के लिए, परीक्षण सॉफ़्टवेयर ढूंढना आवश्यक है जो 64-बिट ऑपरेटिंग सिस्टम पर चल सके।

इसके अलावा, परीक्षण सॉफ्टवेयर को गहरी उप-माइक्रोन प्रक्रियाओं और बढ़ती आवृत्ति के कारण नई परीक्षण समस्याओं का सामना करना पड़ रहा है। अतीत में, ATPG परीक्षण मोड के लिए

स्टैटिक ब्लॉकिंग दोषों का परीक्षण अब लागू नहीं था। पारंपरिक औजारों में कार्यात्मक पैटर्न जोड़ने से नए दोषों को खोजना मुश्किल हो गया। करने का एक बेहतर तरीका है

पिछले कार्यात्मक मोड समूहों को यह निर्धारित करने के लिए वर्गीकृत करें कि किन दोषों का पता नहीं लगाया जा सकता है, और फिर इन लापता दोषों को पकड़ने के लिए एक एटीपीजी मोड बनाएं।

गति से संबंधित समस्याओं का पता लगाने और सर्किट समय को सत्यापित करने के लिए जैसे-जैसे डिजाइन क्षमता बढ़ती है और प्रति ट्रांजिस्टर परीक्षण समय घटता है, एक तुल्यकालिक परीक्षण विधि

नियोजित किया जाना चाहिए। तुल्यकालिक परीक्षण में क्षणिक मॉडल, पथ विलंब और IDDQ सहित कई दोष मॉडल शामिल होने चाहिए।

उद्योग की कुछ कंपनियों का मानना है कि अवरोधन, कार्यात्मक और क्षणिक/पथ विलंब दोषों का संयोजन सबसे प्रभावी परीक्षण रणनीति हो सकती है। गहरे के लिए

सबमाइक्रोन चिप्स और उच्च आवृत्ति संचालन, क्षणिक और पथ विलंब परीक्षण और भी महत्वपूर्ण है।

परीक्षण कोर को सिंक्रनाइज़ करते समय एटीई सटीकता की समस्या को हल करने और लागत को कम करने के लिए, एक नई विधि खोजना आवश्यक है जो इंटरफ़ेस को सरल बनाता है

परीक्षण उपकरण (क्षणिक और पथ विलंब परीक्षण के लिए परीक्षण उपकरण इंटरफ़ेस पर सटीक घड़ी की आवश्यकता होती है), यह सुनिश्चित करता है कि परीक्षण के दौरान संकेत पर्याप्त सटीक है।

चूंकि एसओसी मेमोरी ब्लॉक में निर्माण दोषों की उच्च संभावना है, मेमोरी बीआईएसटी में नैदानिक कार्य होना चाहिए। एक बार समस्या मिलने पर,

दोषपूर्ण पता इकाई को अतिरिक्त पता इकाई की अनावश्यक स्मृति में मैप किया जा सकता है, और पता चला गलती पता हटा दिया जाएगा। फेंकने से बचें

पूरी महंगी चिप।

छोटे एम्बेडेड मेमोरी ब्लॉक का परीक्षण अतिरिक्त गेट्स या कंट्रोल लॉजिक की आवश्यकता को समाप्त करता है। उदाहरण के लिए, वेक्टर रूपांतरण परीक्षण तकनीकें रूपांतरित हो सकती हैं

स्कैन मोड की एक श्रृंखला में कार्यात्मक मोड।

बीआईएसटी विधि के विपरीत, बायपास मेमोरी ब्लॉक के कार्यात्मक इनपुट को अतिरिक्त तर्क की आवश्यकता नहीं होती है। क्योंकि कोई अतिरिक्त परीक्षण तर्क की आवश्यकता नहीं है, SoC

विकास इंजीनियर अतीत में बनाए गए परीक्षण पैटर्न का पुन: उपयोग कर सकते हैं।

उन्नत एटीपीजी उपकरण न केवल समांतर में मैक्रोज़ का परीक्षण करते हैं बल्कि यह भी निर्धारित करते हैं कि क्या कोई विवाद है, साथ ही यह भी विवरण देता है कि कौन से मैक्रो समानांतर में परीक्षण किए जा सकते हैं और कौन से

मैक्रोज़ का समानांतर में परीक्षण नहीं किया जा सकता है। इसके अलावा, मैक्रो क्लॉक स्कैन क्लॉक (जैसे सिंक्रोनस मेमोरी) के समान होने पर भी इन मैक्रोज़ का प्रभावी ढंग से परीक्षण किया जा सकता है।

वर्तमान में, घने दो तरफा बोर्ड पर पर्याप्त परीक्षण बिंदु नहीं हैं, और प्रत्येक जटिल चिप को सीमा स्कैन सर्किट से सुसज्जित किया जाना चाहिए। बिना

बाउंड्री स्कैन, बोर्ड-लेवल मैन्युफैक्चरिंग डिफेक्ट लुकअप काफी मुश्किल हैं और इन्हें ढूंढा भी नहीं जा सकता है। बाउंड्री स्कैन के साथ, बोर्ड-स्तरीय परीक्षण बेहद आसान है

और चिप के भीतर लॉजिक सर्किट्री से स्वतंत्र। बाउंड्री स्कैन एटीपीजी मोड को उत्पादन के किसी भी स्तर पर चिप की स्कैन श्रृंखला में भी कॉन्फ़िगर कर सकता है।